Signal Integrity

Steigende Bandbreiten machen die „Details“ in der digitalen Schaltungsentwicklung immer wichtiger.

Es reicht längst nicht mehr, einfach nur schnellere Taktzeiten zu entwerfen. Mit steigender Frequenz werden die Leiterbahnen auf dem PCB zu mehr als nur einfachen Leitern. Bei niedrigeren Frequenzen weist die "Transmission Line" (Leiterbahn) überwiegend Widerstandscharakteristika auf. Mit zunehmender Frequenz beginnt die Transmission Line, sich wie ein Kondensator zu verhalten. Und bei den höchsten Frequenzen spielt die Induktivität eine immer wichtigere Rolle. All diese Eigenschaften können sich negativ auf die Signalintegrität auswirken.

Bei Geschwindigkeiten ab 600 MHz-Bereich und darüber hinaus kommt es auf jedes Schaltungsdetail an.

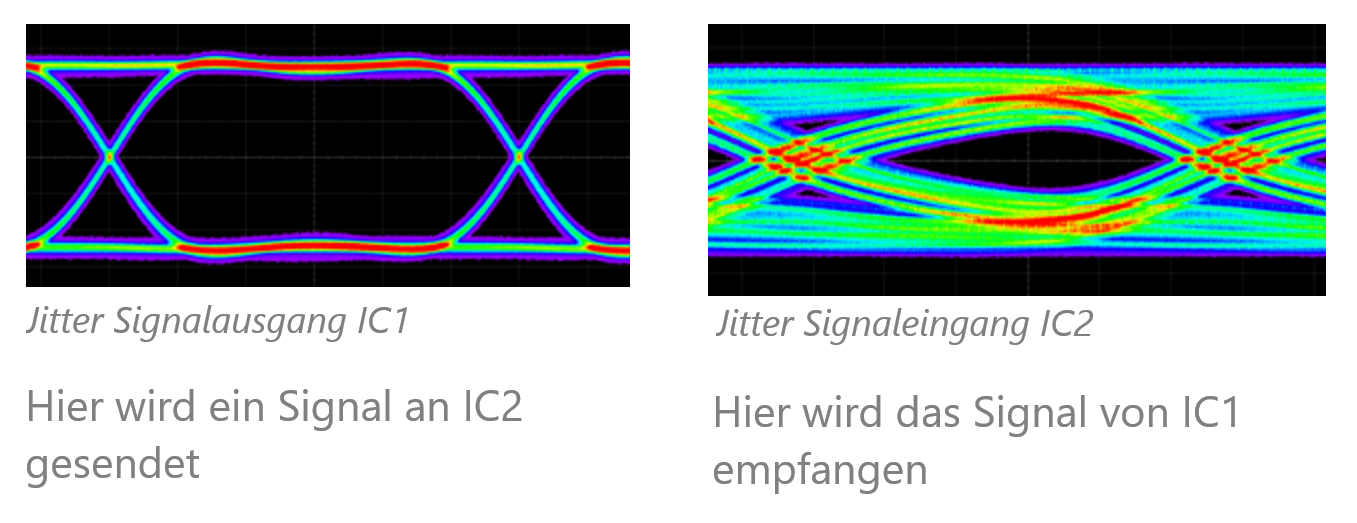

Ein idealer digitaler Puls weist keinerlei Verzerrungen oder Jitter auf und hat schnelle, saubere Übergänge. Mit steileren Flankensteilheiten wird es schwieriger, solche idealen Signalcharakteristika aufrechtzuerhalten. Aus diesem Grunde ist die Signalintegrität ein so wichtiges Thema.

Bei der Signalintegrität geht es darum, wie die elektromagnetischen Felder der Signale mit den Grenzbedingungen der Dielektrika und Leiter interagieren. Oder, aus der Sicht der Schaltung, wie die Spannungen und Ströme der Signale mit den Übertragungsleitungen und Diskontinuitäten der Verbindungen interagieren und von diesen verzerrt werden. Das allgemeine Verfahren, das wir zur Beseitigung von Signalintegritätsproblemen anwenden, besteht darin, dass wir uns zunächst der Probleme bewusst sind, die auftreten könnten, und dann die besten Entwurfsprinzipien anwenden, um sie zu beseitigen. Da es sich bei jedem Produkt um ein individuelles Produkt handelt, bei dem Leistung, Kosten, Risiko und Zeitplan gegeneinander abgewogen werden müssen, müssen wir letztendlich jedes Design einzeln optimieren.

Fokus

- Taktverteilung

- Signalpfadgestaltung

- Leiterbahnstücke

- Rauschpegel

- Impedanz und Last

- Übertragungseffekte

- Signalpfad-Rückströme

- Terminierung

- Entkopplung

- Stromverteilung

Je früher die Schwachstellen oder Fehler im Design gefunden werden, desto kostengünstiger können diese beseitigt werden.

Bei der Signalintegrität ist nicht die Frequenz das Problem, sondern die Übertragungszeit. Sie gibt die Anstiegs- und Abfallzeit digitaler Signale an.

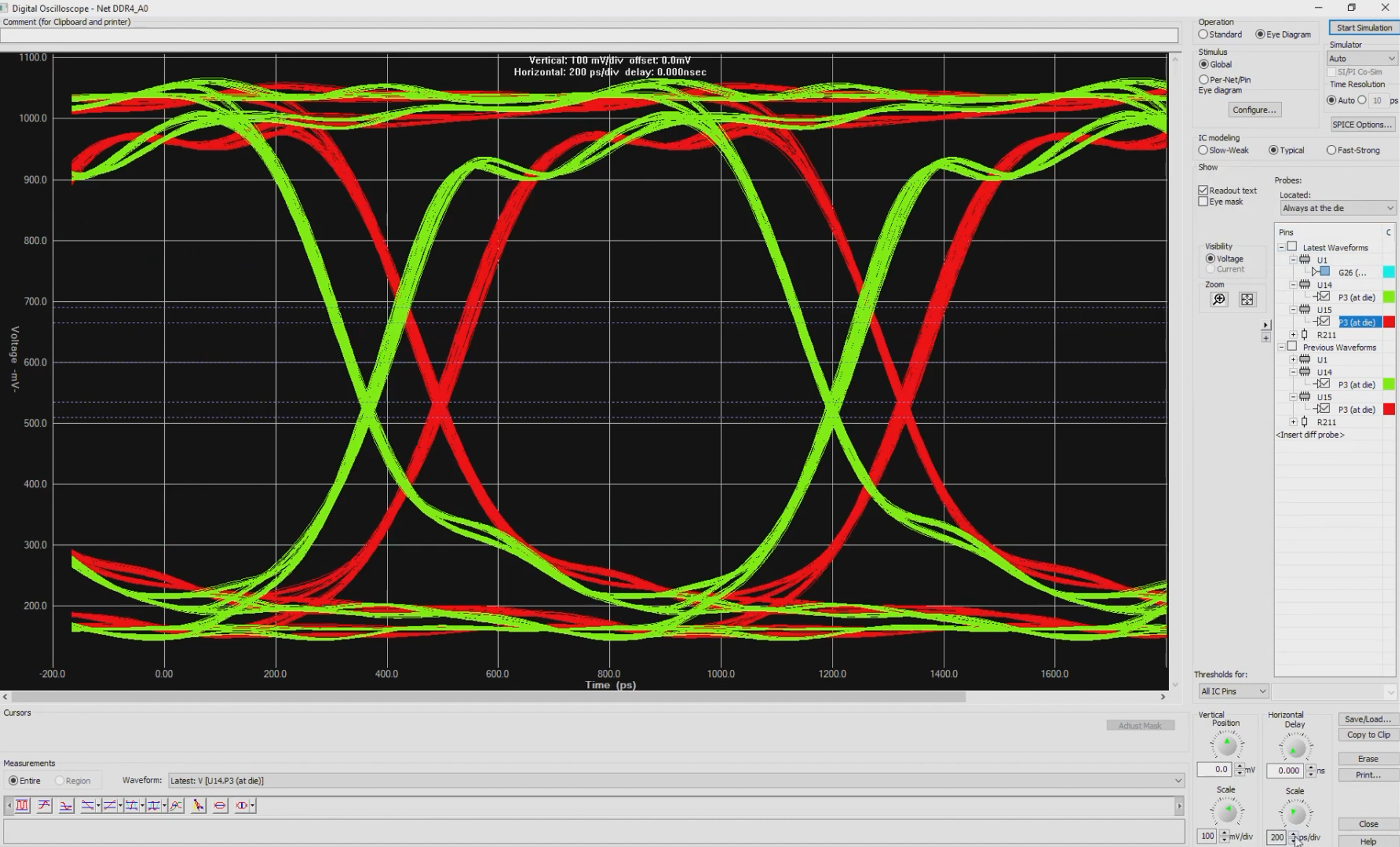

Wir unterstützen Sie diese Schaltungsprobelmatiken anhand von Eye-Diagram, Cross-talk, Reflexionen und der Darstellung elektrischer- & magnetischer Feldlinien zu virtualisieren.

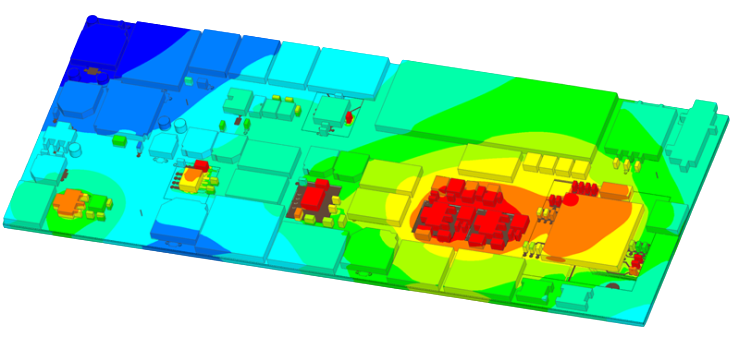

Power Integrity

Power-Integrität ist nichts Neues, wird aber immer wichtiger und wird auch weiterhin die Denkweise von fortschrittlichen Entwicklern beeinflussen. Aber was genau ist Power-Integrität? Sie ist die Beschreibung der Qualität einer Strom- und Spannungsversorgung eines elektrischen Systems. Elektrische Bauteile sind für eine bestimmte Versorgungsspannung ausgelegt, bei der sie fehlerfrei arbeiten. Stabile und saubere Signale auf den Stromversorgungsleitungen sind ein entscheidender Faktor für die Leistungsfähigkeit elektronischer Designs. Hier ist zu erkennen, dass im rot-gelben Bereich am meisten Power benötigt wird und im grünen Bereich es zu einer Spannungsschwankung kommt.

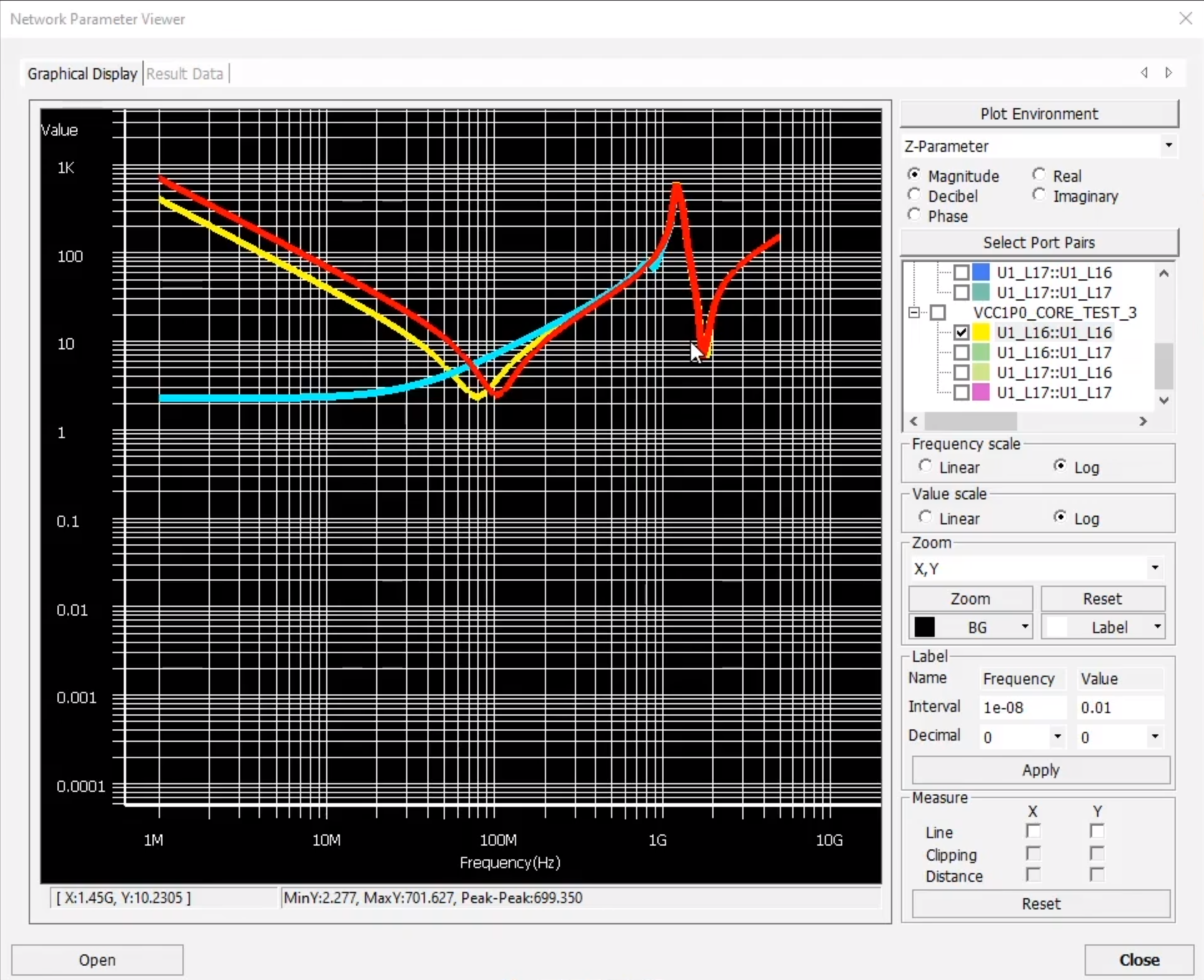

Power Distribution Networks (PDNs) müssen viele rauscharme Planes (Kupfer-Flächen) für empfindliche Lasten wie Mikroprozessoren, DSPs, FPGAs und ASICs bereitstellen. Das Streben nach mehr Geschwindigkeit und höherer Dichte bedeutet schnellere Flankenraten, höhere Frequenzen und mehr Planes mit niedrigeren Spannungspegeln und höheren Strömen. Dies stellt hohe Anforderungen an die Power Integrity des Designs. Das Ziel von Power Integrity Simulationen besteht darin, zu überprüfen, ob die Spannung und der Strom rauscharm und ohne Spannungsabfall die Last erreicht.

Fokus

- PDN Analyse

- Power Ripple

- IR-Drop

- DC-Widerstand

- Spannungsverteilung

- DeCap Effizienz

- Impedance vs. Frequency

- Identifizierung von Hot-Spots

Wenn schnell schaltende aktive Bauteile (ICs) auf dem Board ihren Zustand ändern (typischerweise schalten immer viele I/Os eines ICs gleichzeitig), dann werden parasitäre (Schalt-)Ströme induziert und es entstehen Störspannungsspitzen. Diese können sich im gesamten Versorgungssystem ausbreiten und dann zu funktionalen Fehlern führen und zudem auch das EMV-Verhalten negativ beeinflussen.

Diese Störungen variieren in ihrem Auftreten, da die Energie bekanntlich nicht verschwindet, beeinflussen diese Störung alle umgebenden High-Speed-Funktionen auf dem Board. Störspannungen sind ausserdem effiziente Quellen von EMV-Abstrahlung (sie bilden hochwirksame parasitäre EMV-Antennen).

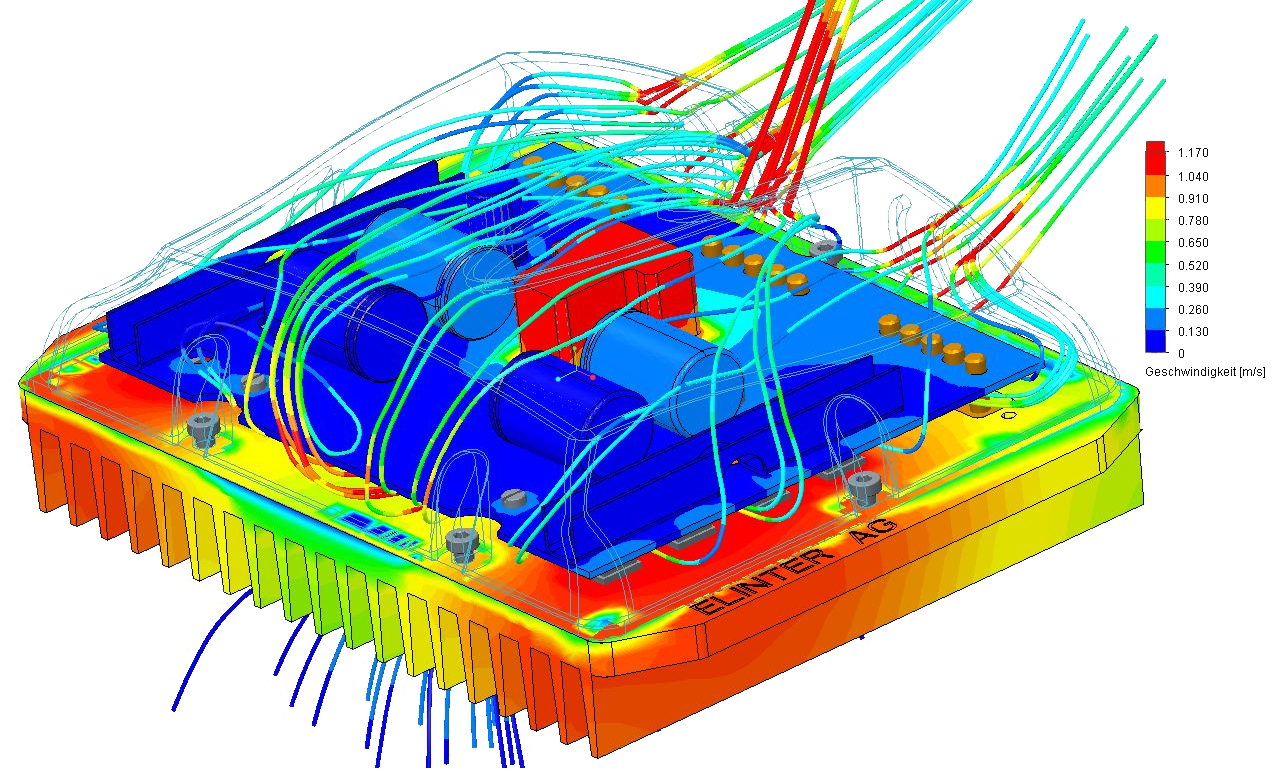

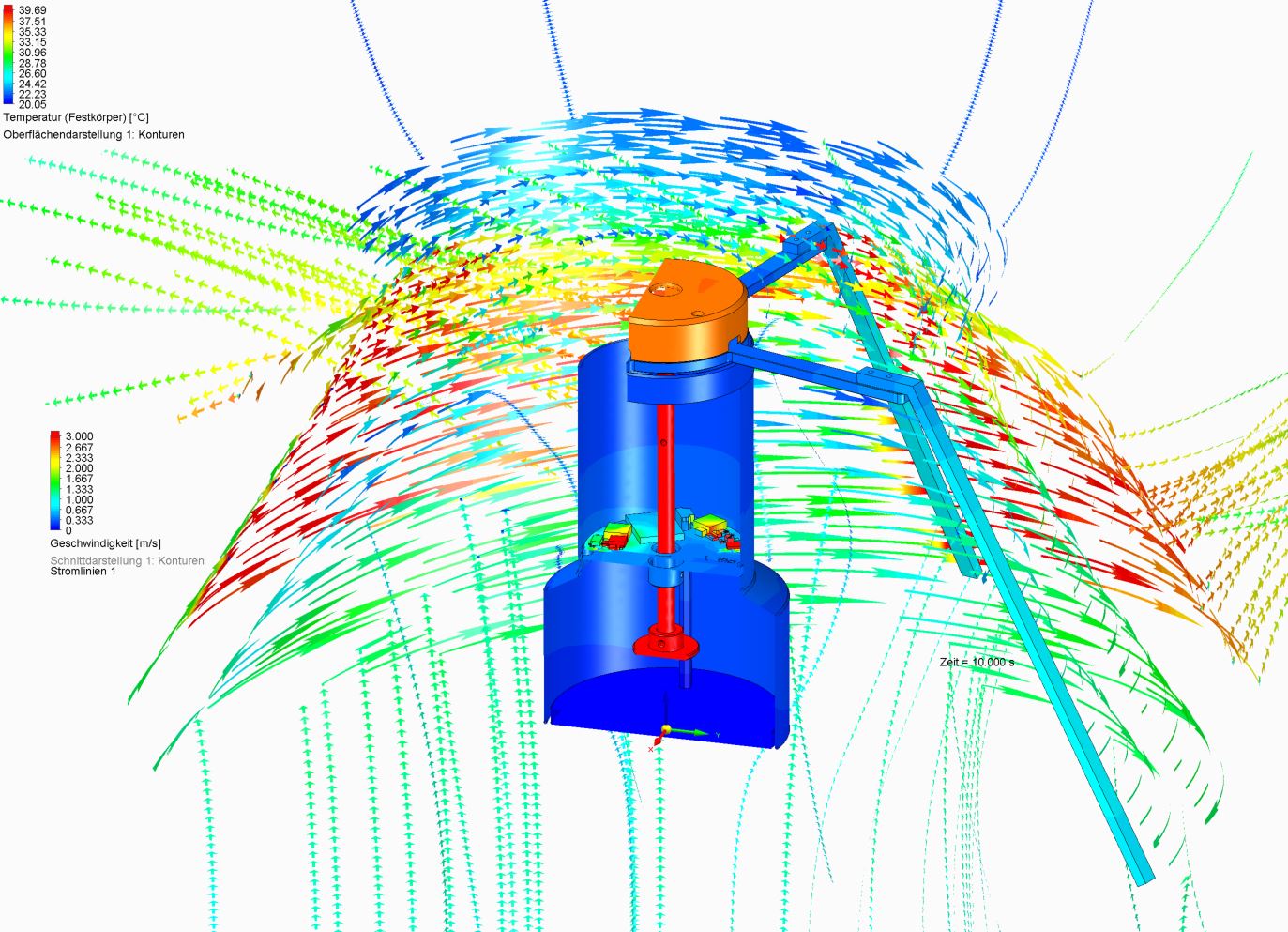

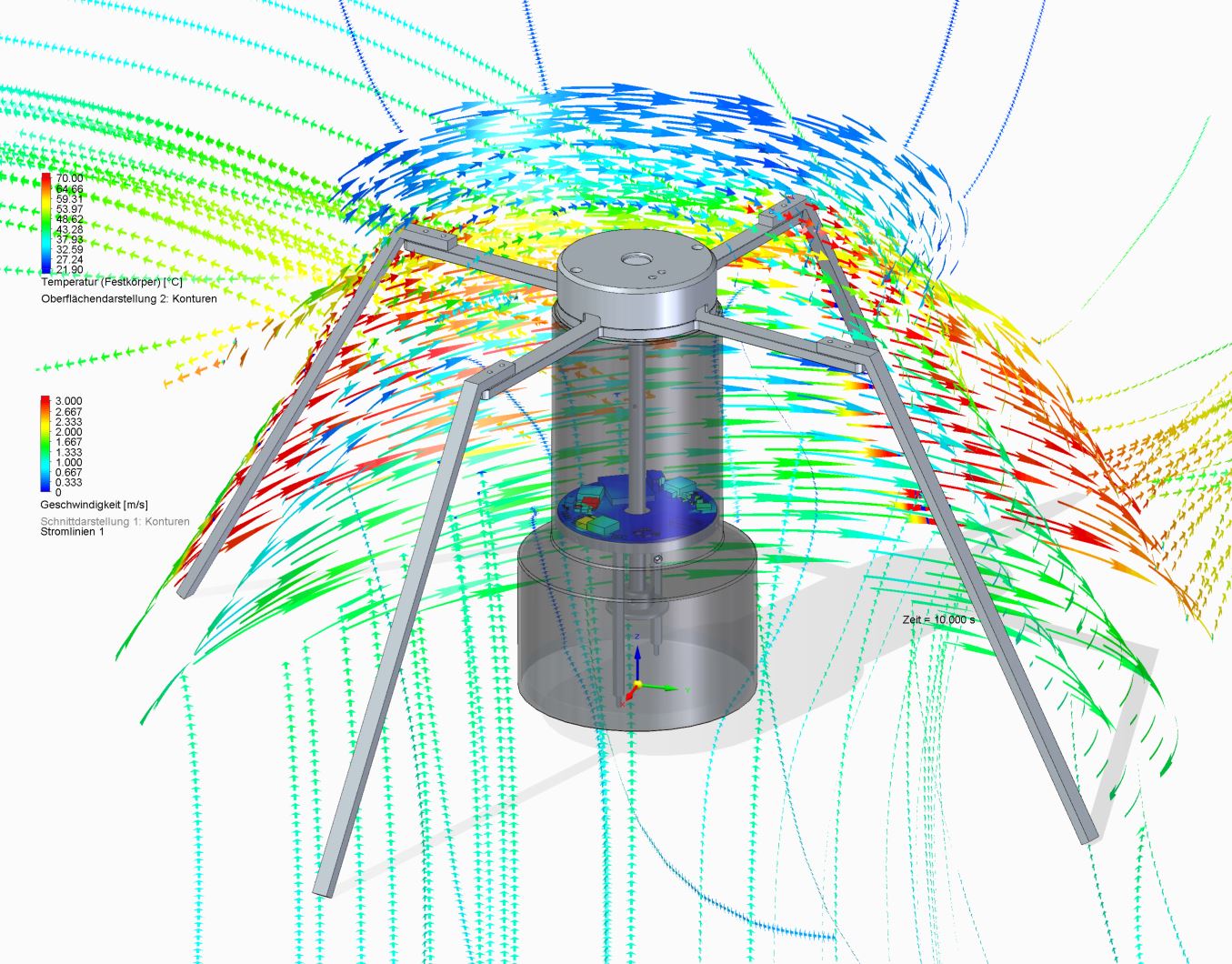

Thermal Analysis

Die Identifizierung der thermischen Wärmekonzentration auf Leiterplatten sowie die Kühlung der Verlustleistung von Komponenten zu einem frühen Zeitpunkt in Design-Workflows, kann teure Herstellung sowie Prüfung von Prototypen ersparen und für eine schnellere Time-to-Market beitragen. Eine sehr schlechte Idee ist meistens „Wir generieren Flächen auf der Leiterplatte für heat spreading!“ Das Problem dabei ist, dass die Signalintegrität der Leiterplatte schlechter sowie auch die EMV unberechenbar wird. Eine Fläche ist nichts anderes als ein magnetischer Dipol, ein magnetischer Dipol ist prädesdiniert für Abstrahlung sowie für das Empfangen von Störsignalen (Schleifenfläche: Der durch eine Leiterschleife fliessende Strom erzeugt ein Magnetfeld, dass sich zum Teil auch um die GND-Plane herum bildet. Damit kann dieses Antennenelement die Störspannungen zur Abstrahlung führen). Mit einer CFD Simulation können schnelle und genaue thermische Abbildungen von Leiterplatten im Gehäuse unter realen Bedingungen simuliert werden. Die Genauigkeit liegt dabei meist zwischen 0.5°C bis 2°C. Die thermische Analyse berücksichtigt sowohl die thermische Simulation der Wärmeleitung durch feste Materialien als auch die Konvektion in der Umgebungsluft. Die thermische Wärmeableitung ist entscheidend für die Leistung und Haltbarkeit der Elektronik. Die effiziente Abführung von Wärme ist für den Betrieb und die langfristige Haltbarkeit von elektrischen Produkten entscheidend.

Was passiert bei Wärme?

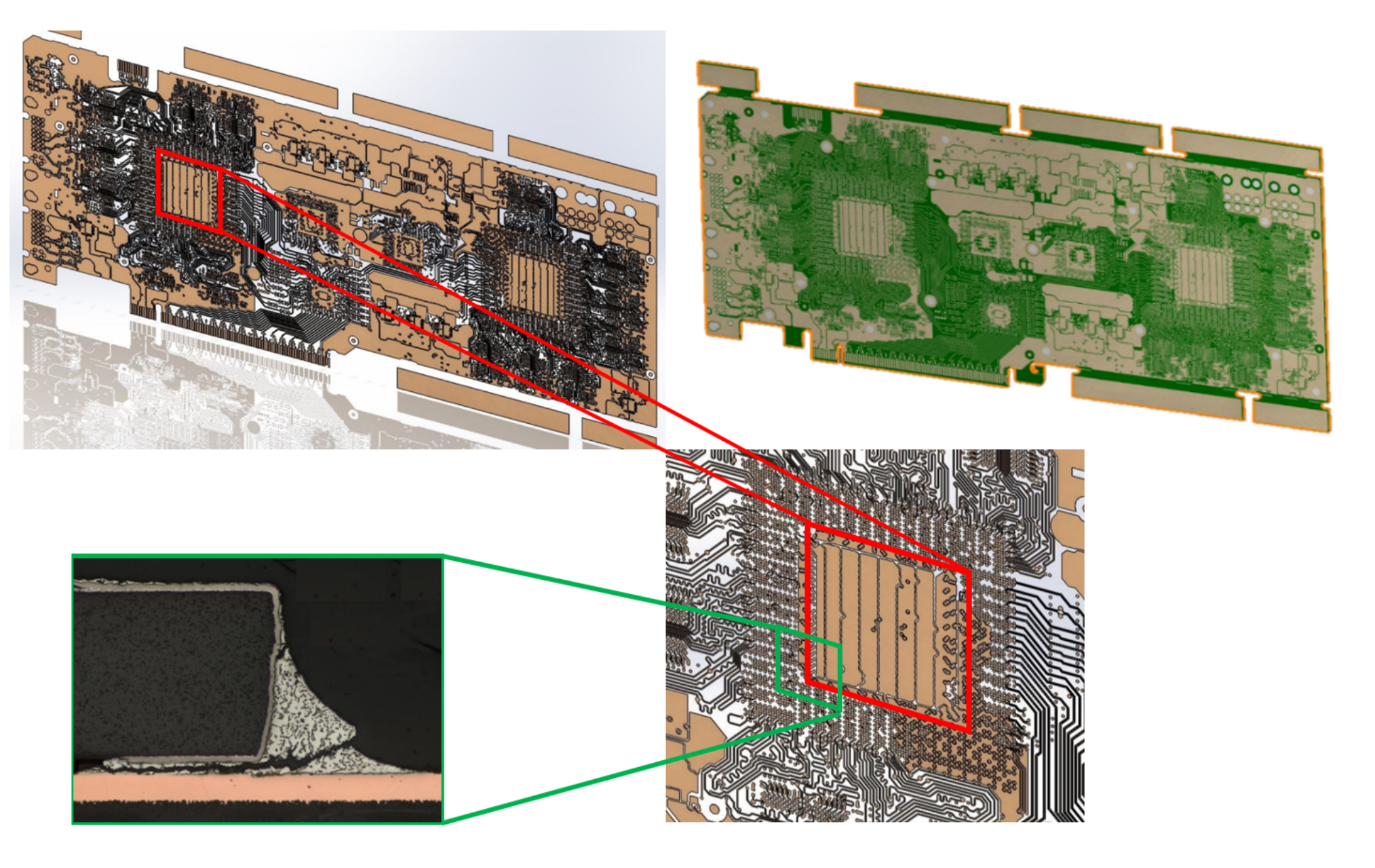

Die Signalintegrität hat indirekt auch mit der Verlustleistung eines ICs resp. FPGAs oder DDR Bauteils zu tun, denn jeder Peak bedeutet mehr (unnötige-) Energie. Steigende Taktfrequenzen und zunehmende Packungsdichte auf dem Siliziumchip, im Package und auf der Leiterplatte sind Ursachen für die stetig steigende Erwärmung. Abgesehen von der Lebensdauer der ICs sowie vereinzelt auch von passiven Bauelementen beginnt sich die Leiterplatte bei Wärme zu dehnen an. Dadurch werden die Lötstellen mechanisch belastet und mit der Zeit spröde. Sobald die Lötstelle spröde wird, brechen die Lötstellen in absehbarer Zeit und es kommt zum berühmten Wackelkontakt.

Datenformate

Welche Daten werden benötigt für eine Analyse der Leiterplatte?

Der Vorteil der Verwendung von CCE oder ODB++ Daten besteht darin, dass der PCB-Stackup und die Kupfergeometrien der Leiterplatte ebenfalls gelesen werden. Dies ist besonders nützlich, wenn thermische Überlegungen wie thermische Durchkontaktierungen oder Kupfergüsse in die Leiterplatte hinein entworfen werden müssen. Ebenso wichtig sind diese Daten für die Überprüfung von EMV gerechten Leiterplatten für eine optimale Signalintegrität. Somit kann ein thermisches Konzept mit EMV Grundgedanken simuliert und entworfen werden.